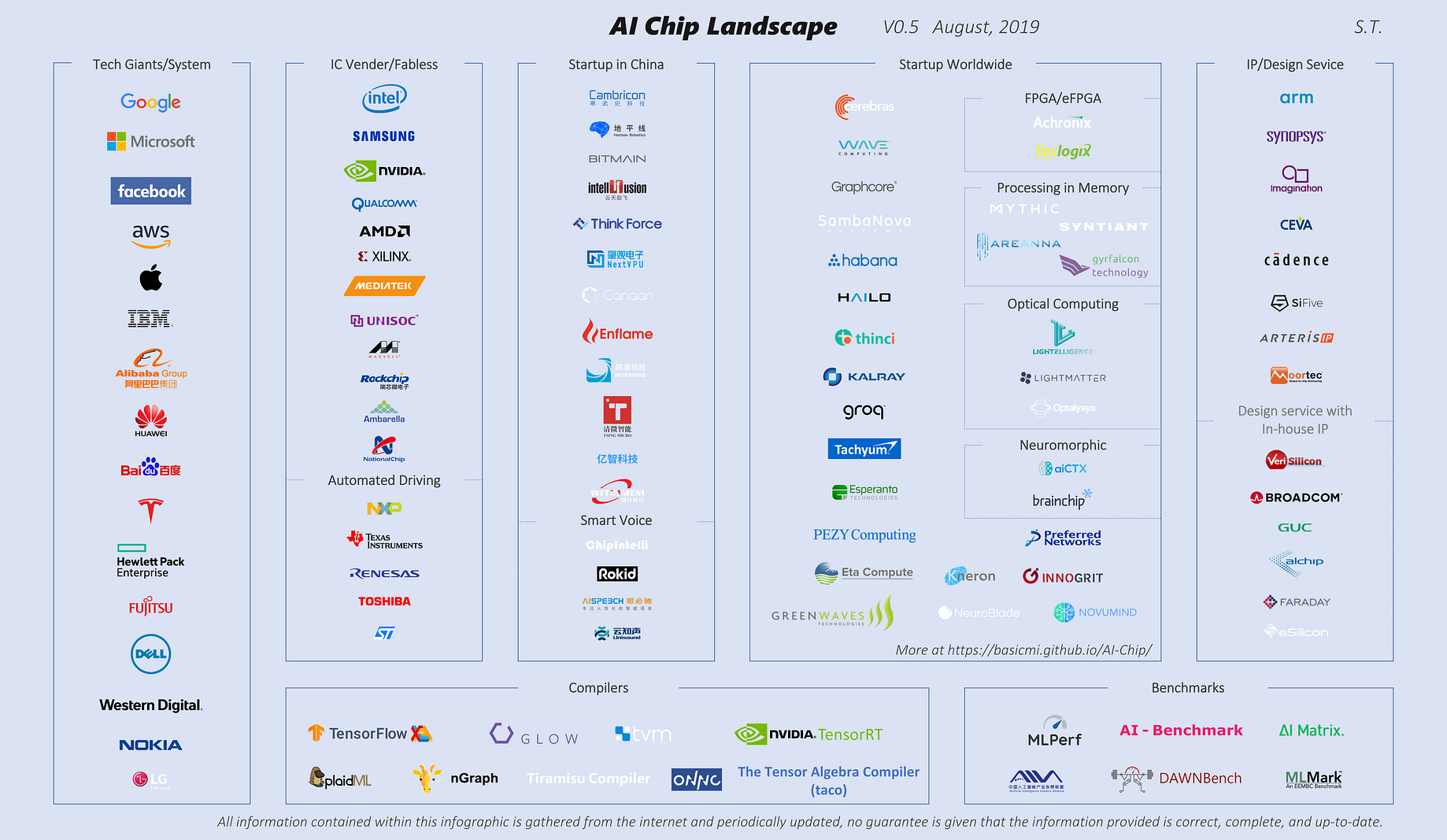

Intel Speeds AI Development, Deployment and Performance with New Class of AI Hardware from Cloud to Edge | Business Wire

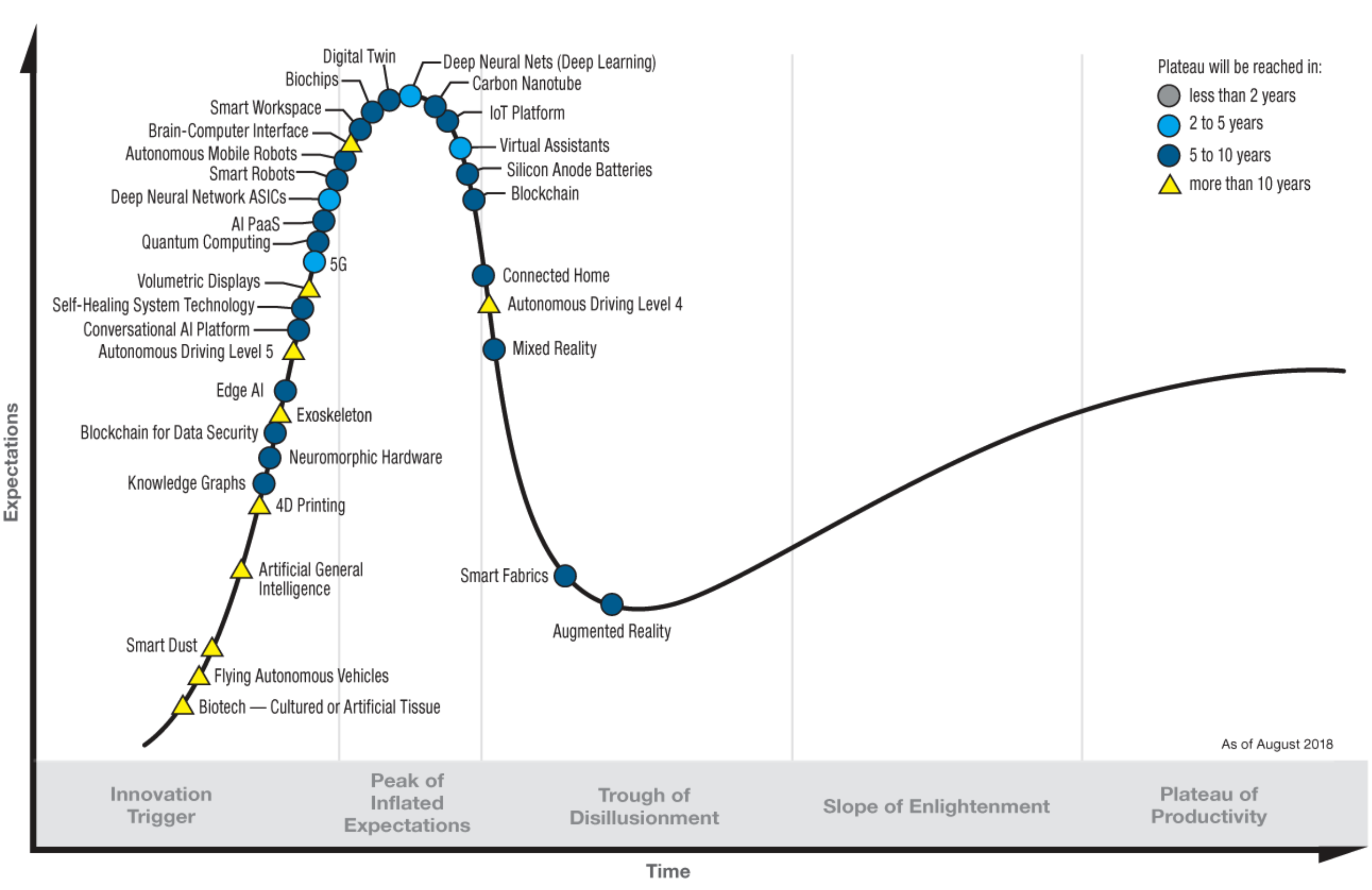

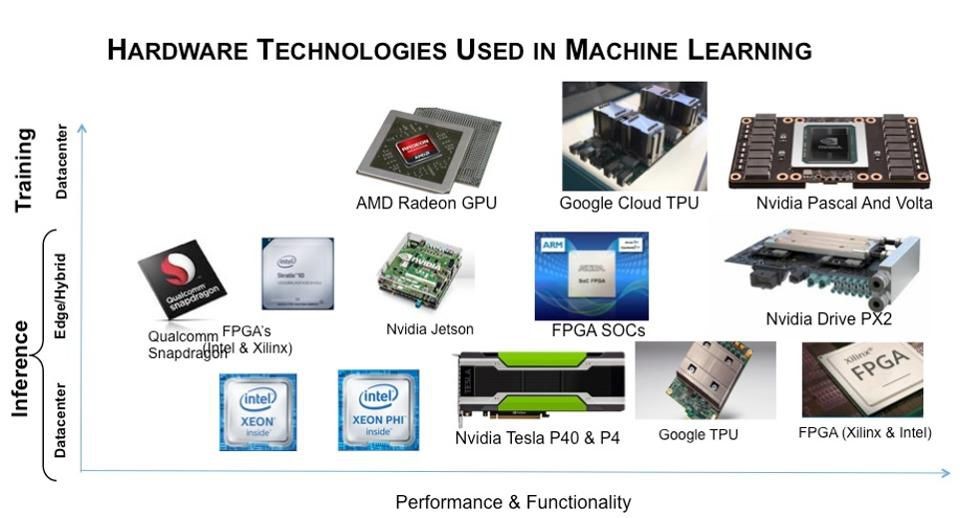

DARPA asks industry for SWaP-optimized machine learning real-time ASICs able to learn from data | Military Aerospace

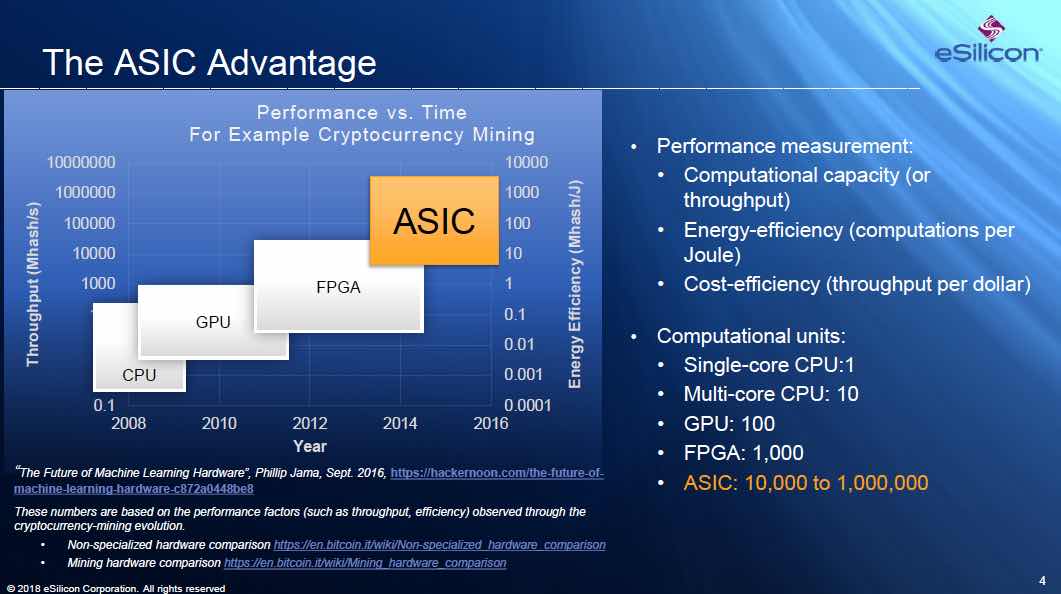

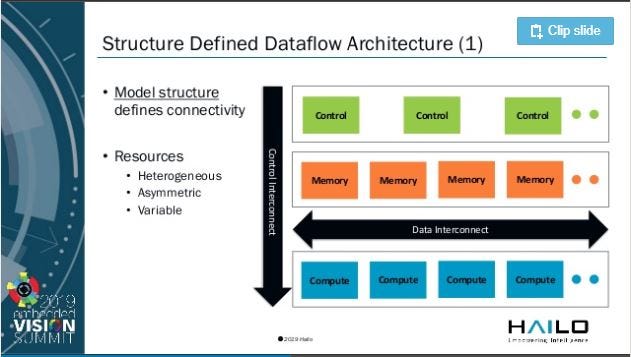

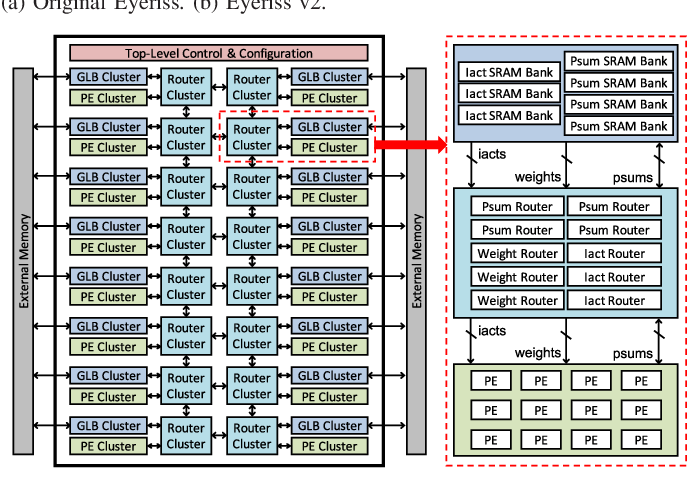

The New Deep Learning Memory Architectures You Should Know About — eSilicon Technical Article | ChipEstimate.com

Deep Neural Network ASICs The Ultimate Step-By-Step Guide: Blokdyk, Gerardus: 9780655403975: Amazon.com: Books

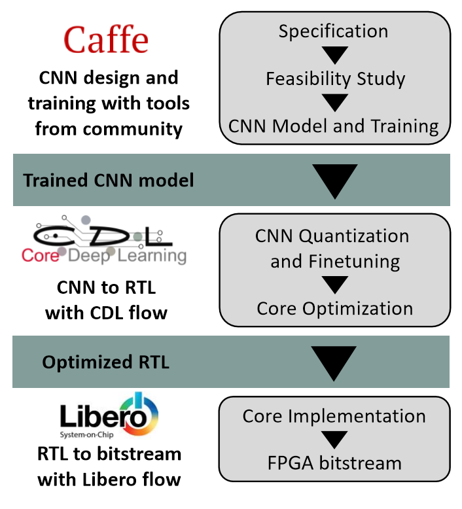

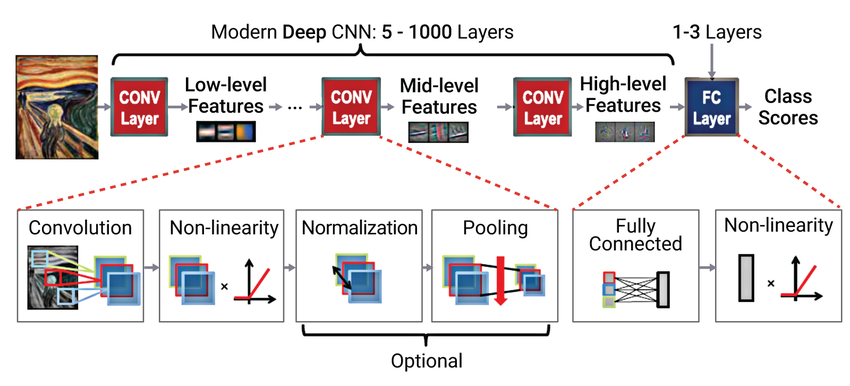

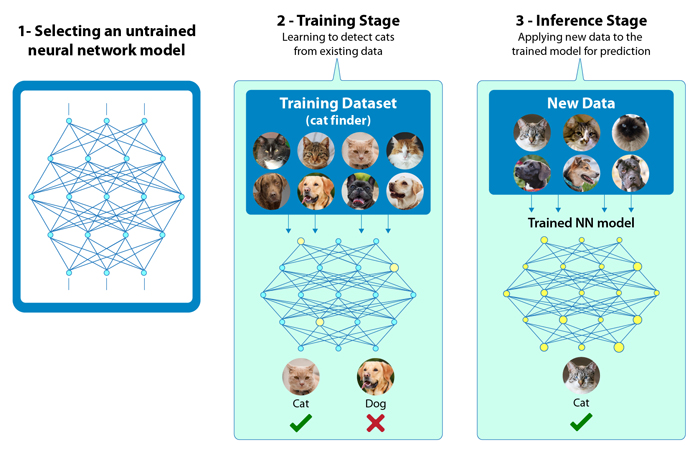

How to develop high-performance deep neural network object detection/recognition applications for FPGA-based edge devices - Blog - Company - Aldec